# データセンターに適した3次元オンチップ型ネットワーク構造の検討と 評価

## 池田崇栄† 大下裕一† 村田正幸†

† 大阪大学大学院情報科学研究科, 吹田市山田丘 1-5 E-mail: †{t-ikeda,y-ohsita,murata}@ist.osaka-u.ac.jp

あらまし データセンターの処理を低消費電力で実現する手法として、データセンター内のサーバー間のネットワークを1チップに集約するオンチップ型データセンターが提案されている。しかしながら既存研究では、2次元格子状にパケット交換スイッチを配置した構造を前提としており、オンチップ型データセンターネットワークに適したネットワーク構造については検討されていない。そこで本稿では、オンチップ型データセンターネットワークに適したネットワーク構造の検討を行う。特に本稿では、近年検討が進められている3次元のネットワーク構造を対象とし、ネットワーク内へのパケット交換スイッチと回線交換スイッチの配置について検討を行う。検討の結果、パケット交換スイッチのみで構成される階層を構築し、そのパケット交換スイッチに各サーバが接続、それ以外の階層は回線交換スイッチのみで構成し、各パケット交換スイッチはすべての階層のスイッチへのリンクを持つ構造が、遅延・消費電力、いずれの観点においても優れていることが明らかとなった。また、その構造では、パケット交換スイッチのみで構成された2次元格子型ネットワークと比べて、消費電力を24%削減、サーバー間の通信遅延を55%削減できることが分かった。

キーワード ネットワークオンチップ、データセンター、消費電力、遅延、3次元オンチップ型ネットワーク

## Evaluation of 3D on-chip network structures suitable to a data center

Takahide IKEDA<sup>†</sup>, Yuichi OHSITA<sup>†</sup>, and Masayuki MURATA<sup>†</sup>

† Graduate School of Information Science and Technology, Osaka University, Osaka, Japan E-mail: †{t-ikeda,y-ohsita,murata}@ist.osaka-u.ac.jp

Abstract In a data center, servers cooperate with each other to handle a large amount of data. As the size of data increases, the energy consumption of the data center increases. To reduce the energy consumption of the data center, an architecture called on-chip data center has been proposed. In this architecture, a large number of CPUs are deployed on a single chip and connected by using Network on Chip (NoC). In this paper, we focus on the 3-D network-on-chip, which reduce the energy consumption compared with 2-D network-on-chip. Then, we deploy packet switches and circuit switches, to accommodate the traffic between servers on the chip efficiently. In this paper, we discuss the network structure by the following points; (1) connection between switches of different layers, (2) the layer of the switches connected to servers, and (3) the arrangement of switches on each layer. We evaluate the energy consumption and the latency between servers. The result clarifies that to reduce the energy consumption and the latency, (1) switches on all layers should be connected to the switch on a certain layer, (2) all servers should connect to the switch on the same layer, and (3) all switches on each layer should be the same kind of switch.

Key words NoC, data center, power consumption, latency, 3D on-chip network

### 1. はじめに

近年、クラウドコンピューティングなど、ネットワークを介

したサービスの多様化にともない、そのサービスを提供する データセンターの重要性が増してきている。データセンターを 用いたサービスが普及・大規模化するにつれ、データセンター の消費電力も大きくなっており、世界で消費される全電力消費の1.1~1.5%を占める[1]など、データセンターの低消費電力化は大きな課題となっている。データセンターの消費電力において、ネットワークが占める割合は少なくなく[2]、データセンターの低消費電力化が必要不可欠である。一方、データセンターではサーバー間の連携によりデータの処理を行っているため、ネットワークの性能はデータセンターの処理性能に大きな影響を与える。そのため、データセンターの性能を維持しつつ、ネットワークの消費電力を削減する方法が必要とされている。

データセンターネットワークの低消費電力化を達成する方法 として、サーバー間の通信需要に合わせて不必要なネットワー ク機器の電源を落とす[3]といった検討が進められている。しか しながら、これらの検討は、既存のデータセンターネットワー クをベースとして、需要の少ない時間帯の消費電力を削減する ことができるのみであり、需要が大きな時間帯の消費電力は依 然高いままである。

低消費電力で高い処理性能を持つデータセンターを構築する手法として、データセンターを一つのチップ上に集約するオンチップ型データセンターが提案されている[4]。オンチップ型データセンターではサーバーの役割を果たす多数の CPU コアと、CPU コア間を結ぶネットワークを1チップに集約する。チップ上に構築されたネットワークは、配線距離が 1mm 以下と著しく小さいため、小さい電力で通信が可能となる[5]。

しかしながら、従来研究では、2次元格子状のネットワークを前提としたオンチップ型データセンターの検討しか行われておらず、オンチップ型データセンターネットワークに適した構造の検討は十分に行われていない。特に近年、チップ上に3次元のネットワークを積層する技術も進展しているため[6]、このような新しい技術を用いることにより、より低消費電力で高性能なデータセンターネットワークを構築できる可能性がある。

そこで、本稿ではネットワークを 3 次元に積層した構造に焦点を当て、オンチップ型データセンターネットワークに適したネットワーク構造について議論する。

#### 2. オンチップ型データセンターネットワーク

回路集積技術の進展により、多数のコアと、そのコア間を結ぶネットワークを1チップに集約することが可能となってきている。オンチップ型データセンター[4]は、このような回路集積技術を用い、多数のサーバーからなるデータセンターを1チップ上で構築する手法である。1チップに集約することにより、サーバー間の配線長を短くすることができ、サーバー間の通信の低消費電力化が実現できる。

オンチップ型データセンターは、CPU やキャッシュメモリなどの機能を果たすコアと、そのコア間を接続するネットワークから構成される。データセンターを構成する要素のうち、大容

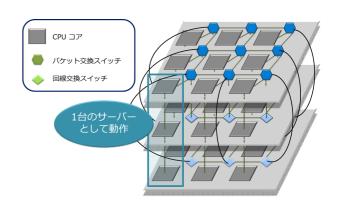

図1 データセンター向け3次元オンチップ型ネットワーク

量の記憶装置などはチップ上に集約することは難しく、集約されたチップの外部に設置され、チップとはインタフェースを通じて読み書きが行われる。

コア間を結ぶネットワークは、回線交換スイッチやパケット 交換スイッチとスイッチ間を結ぶリンクで構成される。回線換 スイッチはパケット交換スイッチと比較して消費電力が小さく なるものの、一つの通信が回線を占有してしまい、他の通信が その回線を使用できない。それに対してパケット交換スイッチ は回線交換スイッチよりも消費電力が大きくなるものの、一つ の回線に複数の通信を収容できる。そのため、それぞれのス イッチの長所を生かした構造が望まれる。

さらに近年は、チップ3次元に積層することで、チップ内に3次元のネットワークを構成する手法も提案されている[6]。3次元のネットワークを構成することにより、多くのコアをより少ない面積に集約でき、消費電力の削減が可能となる。

本稿では、チップ内には3次元のネットワークが構築される ものとし、パケット交換スイッチ・回線交換スイッチを適切に配 置することにより、オンチップ型データセンターに適したネットワーク構造を明らかにする。

## 3. オンチップ型データセンターネットワークに 適したネットワーク構造

### 3.1 検討に用いるモデル

#### **3.1.1** ネットワークモデル

本稿で想定するネットワーク構造を図1に示す。この構造では、3次元に積層されたチップ上に CPU やキャッシュの機能を果たすコアを配置する。異なる階層の同一位置にあるコア同士は直接接続し、一台のサーバーの役割を果たす。コア間を結ぶネットワークは、回路集積の容易な3次元格子型ネットワークであるとする。ネットワークの各ノードは、回線交換スイッチまたはパケット交換スイッチであるとし、各サーバーは、特定の階層において隣接するスイッチ1台と接続することでネットワークと接続する。ただし、各サーバーは同時に複数のサーバーと通信を行う可能性があるため、各サーバーと接続するスイッチはパケット交換スイッチであるとする。

#### 3.1.2 電力消費モデル

チップ上に構成されたネットワークが消費する電力は、ネットワーク構造や、流れるトラヒック量、トラヒックに含まれる ビット反転の数によって決まる。

文献 [5] では、16 bit 幅のリンクを用いて構成した 2 次元格子型のチップ上に構成したネットワークにおいて、5 割のビットが反転するトラヒックが流れた際に、回線交換スイッチ、パケット交換スイッチ、スイッチ間のリンクで消費される電力を測定し、モデル化を行っている。その結果、トラヒック 1 bit あたりの消費電力は、回線交換スイッチで  $0.37~\mu W$ 、パケット交換スイッチで  $0.98~\mu W$ 、リンクで  $(0.39+0.12L)~\mu W$ (ただし L はリンクの長さ (mm)) であることが明らかになっている。本稿では、このモデルを用いることにより、ネットワークの消費電力を評価する。

本稿では、ネットワークの消費電力に注目するため、各コア の消費電力を計算に含めず、各リンク、回線交換スイッチ、パ ケット交換スイッチで消費される電力の合計の比較を行う。

チップ上の各スイッチの消費電力やリンクの消費電力は、用いるスイッチの構造やスイッチ間のリンクの帯域によって異なる。しかしながら、どのような構造を採用した場合であっても、パケット交換スイッチは回線交換スイッチよりも複雑な処理が必要となり、その消費電力は大きくなる。そのため、各スイッチやリンクの消費電力が異なる他の構造においても、本稿の検討・考察は適用可能である。

#### 3.1.3 遅延モデル

本稿では、各サーバー間に同時に発生するトラヒック要求を 生成し、その要求されたトラヒックをすべて転送し終えるまで にかかる時間を計算することにより、ネットワーク内で発生す る遅延の比較を行う。

チップ上に構成されたネットワークでは、パケットをより小さな単位に分割されたフリット単位で転送処理が行われることが一般的である。本稿では、隣接するパケット交換スイッチで1フリットが転送されるのに1クロック要するものとして、トラヒック要求を転送し終わるまでのクロック数を計算し、比較する。パケット交換スイッチが1フリット転送する際にかかるクロック数は、パケット交換スイッチの構成により異なる。しかしながら、1フリット転送する際にかかるクロック数が変化した場合であっても、遅延の観点で評価したネットワーク構造の優劣は変化しない。そのため、本稿での議論は、異なるパケット交換スイッチを用いたネットワークにおいても適用可能である。

また、本稿で検討するネットワークは、パケット交換スイッチのみではなく、回線交換スイッチも用いている。回線交換スイッチは、事前に出入口ポートの設定を行う。そのため、回線交換スイッチを経由して接続されたパケット交換スイッチ間で

は、隣接するパケット交換スイッチへのフリットの転送と同様 のフリットの転送が可能となる。本稿では、回線交換スイッチ の経由には、クロック数を要しないとし、発生した通信が経由 するパケット交換スイッチのみで、サーバー間の通信にかかる クロック数が決まるものとした。

#### **3.1.4** トラヒックモデル

検討で用いるトラヒックモデルは特定サーバー間通信とし、これは、データセンター内で複数の処理を並列に動作している場合に相当し、各データの処理に関係した特定のサーバー間のみで通信が発生する。本稿では通信を行うサーバーペアをランダムに選択し、選択されたサーバー間で1000 bit のトラヒック需要が発生するものとし、通信を行うサーバーペアの数を変化させて評価を行った。

#### 3.1.5 経路計算モデル

本稿では、消費電力を基準として定めたコア間のトラヒック の経路を用いて検討・評価を行う。

3.1.2 の電力消費モデルより、各スイッチ、リンクが消費する電力は、経由するトラヒック量に依存する。そのため、トラヒック需要の多いサーバーペア間の通信が消費電力に与える影響は大きく、1 bit あたりの消費電力がより少ない経路に収容することが必要とされる。

そこで、本稿では、サーバーペアに発生している通信需要が多いものから順に経路を確定する。3.1.2のモデルでは、各スイッチ・各リンクが使用する消費電力は、そのスイッチ・リンクを流れるトラヒック量に比例するため、各サーバーペアに対する低消費電力な経路は、各スイッチ・リンクの1bitあたりの消費電力を重みとしたグラフ上でダイクストラ法を用いて得ることができる。ただし、経路計算の際には、すでに設定済みの回線交換スイッチの出入口ポートは、接続されているものとして扱う。

上述の経路計算モデルでは、入力としてサーバーペア間のトラヒック需要が必要となり、集中的な経路計算が必要となる。本稿における適切なネットワーク構造の比較・検討では、効率的な経路計算が可能であるという条件のもとで、低消費電力・低遅延でサーバー間トラヒックが収容可能なネットワーク構造を明らかにすることを目的としており、このような集中型の経路計算手法を適用した場合に達成できる遅延・消費電力の比較を行っている。しかしながら、実際のチップ上のネットワークでは、集中的な経路計算やサーバーペア間のトラヒック需要を事前に知ることは困難である。集中的な経路計算が不要で、経路計算時にトラヒック需要が不明でも動作可能な経路計算手法は今後の課題である。

#### 3.2 検討項目

3次元格子型ネットワークを用いたオンチップ型データセンターネットワークでは階層間をどのように接続するのか、サー

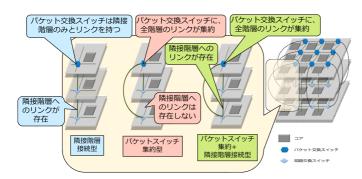

図 2 検討に用いる階層間の接続構造

バーをどの階層でスイッチと接続するのか、階層内をどのように接続するのかの3点を定めることにより、ネットワーク構成を定めることができる。本稿ではそれぞれ階層間の接続、サーバー・スイッチ間の接続階層、階層内の接続として比較と検証を行う。

#### 3.2.1 階層間の接続

異なる階層に属するスイッチの接続方法としては図 2 に示すように、(1) 隣接階層のスイッチ同士を接続する(隣接階層接続型)、(2) 全階層の回線交換スイッチをすべて一台のパケット交換スイッチと接続する(パケットスイッチ集約型)、(3) 隣接階層のスイッチ同士を接続した上で、全階層の回線交換スイッチと一台のパケット交換スイッチを接続する(パケットスイッチ集約+隣接階層接続型)の3種類が考えられる。

隣接階層接続型は、ポート数の多いスイッチは不要であるものの、離れた階層のスイッチを経由するためには、複数階層のスイッチを経由する必要が生じる。それに対して、パケットスイッチ集約型は、全階層と接続しているパケット交換スイッチが存在するため、いずれの階層へも1ホップで到着可能であり、全階層を有効に利用した通信が可能となる。パケットスイッチ集約+隣接階層接続型は隣接階層接続型のリンクとパケットスイッチ集約型のリンクを併せ持った構造であり、各サーバー間に多数の経路を確保することが可能となる。しかしながら、他の構造の2倍の数の階層間のリンクが必要となる。

本稿では、上記の3種類のネットワーク構造と、2次元格子 状にパケット交換スイッチを配置したネットワーク構造(2次元格子型)の比較を行うことにより、適切な階層間の接続構造 を明らかにする。本比較では、第一階層はサーバーと直接接続 したパケット交換スイッチのみを配置し、第二階層以降には、 回線交換スイッチを配置するものとする。

## 3.2.2 サーバーとスイッチの接続階層

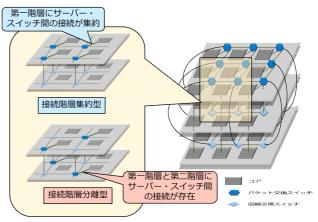

本稿では、各サーバーはいずれかの階層において、パケット 交換スイッチと接続することにより、ネットワークに接続する。 図3に示すように、サーバー・スイッチ間の接続を同一階層に 集約する構造(接続階層集約型)、サーバー・スイッチ間の接続 階層が異なる構造(接続階層分散型)の2通りの、サーバーを

図3 検討に用いるサーバーとスイッチの接続階層

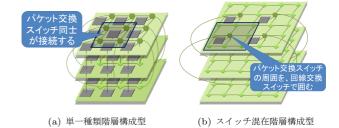

図 4 検討に用いる階層内の配置構造

ネットワークに接続する方法が考えられる。

接続階層集約型は、全サーバーが同一階層のスイッチと接続しているため、サーバー間のホップ数を小さくすることができる。それに対して、接続階層分散型は、ホップ数は大きくなるものの、サーバー間に回線交換スイッチを経由した複数の経路を確保できるため、低消費電力な経路が見つかる確率が高くなると考えられる。

#### 3.2.3 階層内の配置

階層内の配置構造としては、図 4(a) に示すように、パケット 交換スイッチのみを配置した層を構成する(単一種類階層構成 型)、図 4(b) に示すように、パケット交換スイッチと回線交換 スイッチを混在させる(スイッチ混在階層構成型)という 2 つ の構造が考えられる。

スイッチ混在階層構成型では、単一種類階層構成型と比べ、 サーバー間の経路数が多くなるため、低消費電力な経路を発見 できる可能性がある。ただし、サーバー間のホップ数や配線長 は増加する。

本検討では、単一種類階層構成型とスイッチ混在階層構成型の比較を行うことで、パケット交換スイッチ同士を接続した階層があったほうがよいのか、それとも、回線交換スイッチを用いてパケット交換スイッチ間の経路にも冗長性を持たせた方がよいのかを明らかにする。

#### 3.3 検討結果と考察

格検討において、階層数 5、各階層のサーバー数とスイッチ 数は横方向 15、縦方向 15 の合計 225 の場合について発生させ

(a) 階層内の配置の違いによる消費電 (b) 階層内の配置の違いによる遅延の カの変化 変化

図 5 階層間の接続における検討結果

るトラヒックをランダムに変更して評価を行い、それらの平均 値をグラフに示した。

#### 3.3.1 階層間の接続の検討

本小節では、階層間の接続構造が異なるネットワーク構造を消費電力の観点から比較を行う。消費電力の比較を図示したグラフを図5(a)に示す。ただし、図の縦軸は2次元格子型ネットワークにおける消費電力を100として正規化した値である。

図 5(a) より、3 次元格子型で構成した 3 種類の接続型は 2 次元格子型と比べ、通信を発生させたサーバーペアの数が少なければ少ないほど、削減できる消費電力は大きい事がわかる。これは、通信を発生させたサーバーペアの数が少ない場合は、回線交換スイッチのみを経由した径路が見つかりやすく、消費電力が大きいパケット交換スイッチを経由するトラヒックを大きく削減できるためだと考えられる。それに対して、通信が発生するサーバーペアの数が多い場合は、回線交換スイッチのみを用いた経路を見つけることができないトラヒックが多く発生し、複数のパケット交換スイッチを経由するトラヒックが増加してしまう。その結果、消費する電力は、2 次元格子型と同程度となる。

また、隣接階層接続型よりもパケットスイッチ集約型の方が 消費電力が少ないことが分かる。これは、隣接階層接続型では、 第三階層の回線交換スイッチを利用するには、第二階層の回線 交換スイッチも経由する必要があるためである。そのため、第 二階層の回線交換スイッチが全て使用されている場合、第三階 層の回線交換スイッチにたどり着くことができず、第三階層以 降の回線交換スイッチを効率的に利用することができない。そ れに対して、パケットスイッチ集約型では、パケット交換スイッ チが全階層に直接接続しているため、全階層の回線交換スイッ チを利用することができ、より低消費電力の経路を見つけるこ とが可能となる。

図 5(b) に遅延の比較結果を示す。この図でも図 5(a) と同様、2 次元格子型の遅延を 100 として正規化を行っている。図 5(b) より、3 次元格子型で構成した 3 種類の接続型は 2 次元格子型の遅延と比較して、遅延を 4 割~5 割削減できることが分かる。

(a) サーバーとスイッチの接続階層の (b) サーバーとスイッチの接続階層の 違いによる消費電力の変化 違いによる遅延の変化

図 6 サーバーとスイッチの接続階層における検討結果

これは、回線交換スイッチを用いることにより、各サーバーペア間の通信が経由するパケット交換スイッチの数を減らすことができているためだと考えられる。その結果、より少ないクロック数で、宛先サーバーまで到達可能となる。

また、パケットスイッチ集約型の方が、隣接階層接続型より も遅延を抑えることができている。これは、消費電力と同様 に、隣接階層接続型では、パケット交換スイッチから離れた階 層の回線交換スイッチを利用することができないのに対して、 パケットスイッチ集約型では、いずれの階層の回線交換スイッ チも利用した径路を用いることができるためである。その結果、 パケットスイッチ集約型は、経由するパケット交換スイッチの 数をより多く削減でき、遅延を削減可能である。

以上より、階層間の接続においては、ある階層のパケット交換スイッチに全階層の回線交換スイッチが接続する構造が良いと考えられる。

## 3.3.2 サーバーとスイッチの接続階層の検討

本小節では、サーバーが接続するスイッチが属する階層の違いによる消費電力・遅延を評価する。

図 6(a) に消費電力の比較を示す。ただし、図の縦軸は2次元格子型ネットワークにおける消費電力を100として正規化した値である。図 6(a) より、接続階層集約型は2次元格子型よりも低い消費電力を達成できるのに対して、接続階層分散型は2次元格子型よりも消費電力が大きくなることが分かる。これは、接続階層分散型では、隣接サーバー間のホップ数が2次元格子型よりも著しく大きいことが原因である。

図 6(b) に遅延の比較を示す。ただし、図の縦軸は 2 次元格子型ネットワークにおける遅延を 100 として正規化した値である。図 6(b) より、接続階層分散型は 2 次元格子型よりも遅延が大きくなっていることが分かる。これは、消費電力の場合と同様に、各サーバーが接続するスイッチの階層が分散することにより、サーバー間のホップ数が増大してしまうことが原因であると考えられる。

以上より、接続階層分散型は消費電力、遅延ともに2次元格 子型よりも悪化するため、サーバーと接続するスイッチは特定

(a) 階層内の配置の違いによる消費電 (b) 階層内の配置の違いによる遅延の カの変化 変化

図 7 階層内の配置における検討結果

の階層に集約する構造が良いと考えられる。

#### 3.3.3 階層内の配置の検討

本小節では、各階層は一種類のスイッチで統一するべきか、 パケット交換スイッチと回線交換スイッチを混在させた方がよいのかについて検討を行う。

図 7(a) に消費電力の比較を示す。ただし、図の縦軸は 2 次元格子型ネットワークにおける消費電力を 100 として正規化した値である。図 7(a) より、スイッチ混在階層構成型の消費電力は 2 次元格子型よりも悪化していることが分かる。これは、スイッチ混在階層構成型では、パケット交換スイッチの周囲を回線交換スイッチで囲む構造となっているため、サーバー間のホップ数が増大することが原因である。

図 7(b) に遅延の比較を示す。ただし、図の縦軸は 2 次元格子型ネットワークにおける遅延を 100 として正規化した値である。図 7(b) より、スイッチ混在階層構成型よりも単一種類階層構成型の方が、より遅延を短くすることができているとわかる。これは、スイッチ混在階層構成型ではパケット交換スイッチ同士が直接接続されていないため、回線交換スイッチの設定によっては、実際には隣接するサーバー間の通信であっても、大回りした径路しか確保できず、経由するパケット交換スイッチ数が増加することがあることが原因である。それに対して、単一種類階層構成型では、隣接するパケット交換スイッチ同士が直接接続している。そのため、通信するサーバーペア数が増え、利用可能な回線交換スイッチがない場合でも、2 次元格子型と同じ経路は存在し、経由するパケット交換スイッチの数が極端に大きい経路は存在しない。その結果、単一種類階層混成型はより少ない遅延でサーバー間を接続可能となる。

以上より、スイッチ混在階層構成型と比較して単一種類階層 構成型の消費電力が小さく、また遅延も常に低く抑えられてい ることから、各層は同種のスイッチで統一する構造の方が消費 電力と遅延の両方の面で優れていると考えられる。

### 4. 終わりに

本稿では、データセンターのための3次元オンチップ型ネットワーク構造について消費電力と遅延の観点から評価を行った。評価の結果、各サーバーが直接接続するパケット交換スイッチを同一階層に配置した上で、同一階層内はパケット交換スイッチ、あるいは回線交換スイッチで統一し、階層間は同一位置のパケット交換スイッチと全階層の回線交換スイッチを接続する構造が、最も消費電力量と遅延を削減できることが明らかになった。また、削減できる消費電力量は通信を行うサーバーペア数に依存し、通信を行うサーバーペア数が増加すると、回線交換スイッチのみを用いた経路を見つける事ができないサーバーペア間が増加し、削減できる消費電力量の割合が小さくなることも明らかとなった。

今後はデータセンターのためのオンチップ型ネットワークに 適した経路制御手法を検討する予定である。

謝辞 本研究を行うにあたり、奈良工業高等専門学校情報工学科の井上一成教授には適切な助言を頂きました。心よりお礼申し上げます。また、本研究の一部は、文部科学省科学研究費補助金若手研究(B)23700077によっています。

#### 対 対

- J. G. Koomey and P. D, "Growth in data center electricity use 2005 to 2010," The New York Times, Aug. 2011.

- [2] D. Abts, M. Marty, P. Wells, P. Klausler, and H. Liu, "Energy proportional datacenter networks," in *Proceedings of the International Symposium on Computer Architecture*, pp. 338–347, June 2010.

- [3] B. Heller, S. Seetharaman, P. Mahadevan, Y. Yiakoumis, P. Sharma, S. Banerjee, and N. McKeown, "Elastictree: Saving energy in data center networks," in *Proceedings of USENIX*, pp. 17–32, Apr. 2010.

- [4] M. Kas, "Toward on-chip datacenters: a perspective on general trends and on-chip particulars," The Journal of Super-computing, vol. 62, pp. 214–226, Oct. 2012.

- [5] P. T. Wolkotte, G. J. M. Smit, N. Kavaldjiev, J. E. Becker, and J. Becker, "Energy model of networks-on-chip and a bus," in *Proceedings of IEEE International Symposium on* System-on-Chip, pp. 82–85, Nov. 2005.

- [6] F. Li, C. Nicopoulos, T. Richardson, and Y. Xie, "Design and management of 3D multiprocessors using network-inmemory," in *Proceedings of ISCA*, pp. 130–141, June 2006.